ELECTROPLATING SERVICE

ELECTROPLATING SERVICE

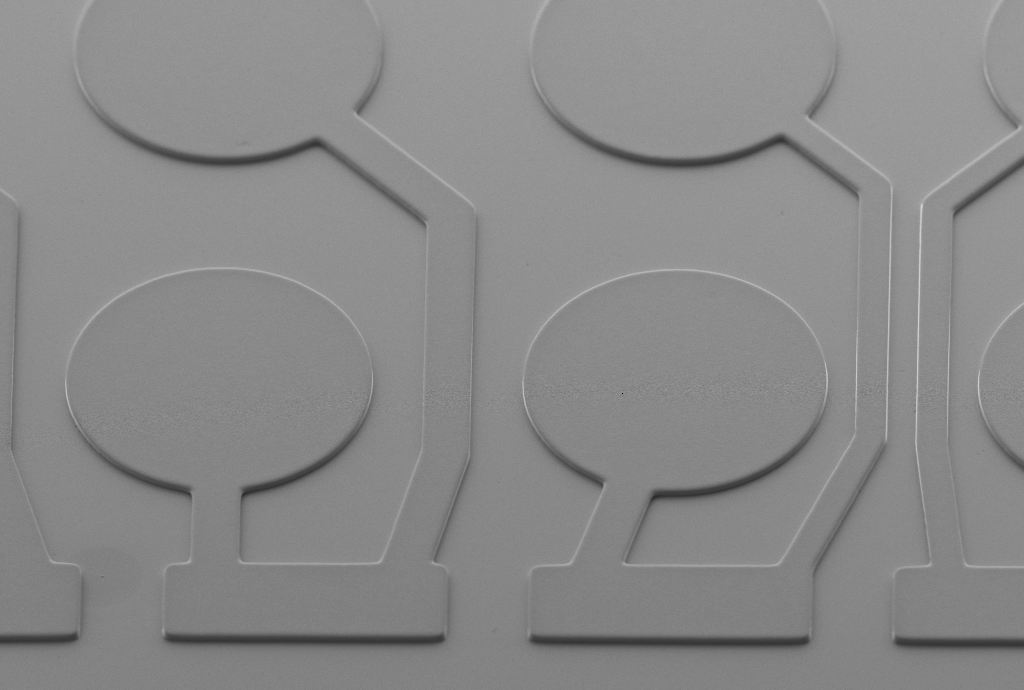

Wafer Level Chip Scale Packaging (WLCSP) is becoming more prevalent as industry demands smaller and thinner microelectronic packages. WLCSP allows smaller form factors, improved electrical performance and a relatively simpler structure over conventional wire bond or interposer packaging technologies. PacTech offers state-of-the-art wafer bumping and WLCSP solutions such as RDL and copper pillar plating: