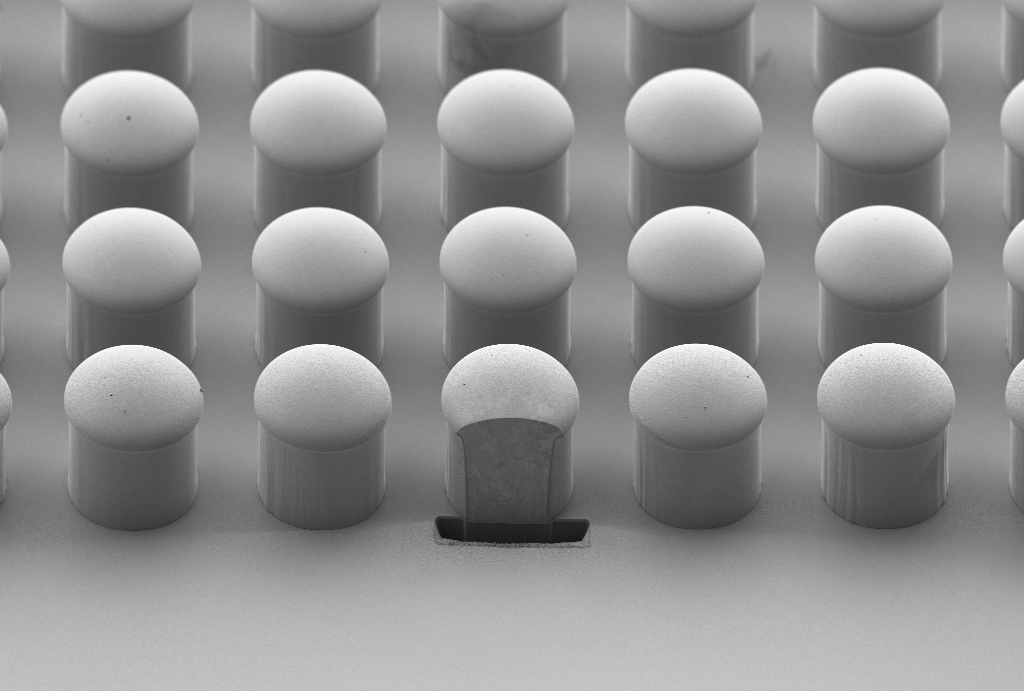

Kupfersäulen für das Wafer Level Packaging

Die fortschrittliche Packaging-Roadmap verlangt nach kleineren Pitches und Bump-Durchmessern bei gleichbleibender Gehäusehöhe. Cu-Pillar-Bumping kann die Nachfrage nach einer Verfeinerung der Gehäusegröße mit besserer Elektromigrationsleistung erfüllen, zusammen mit anderen Vorteilen wie RoHS-Konformität, höherer Kosteneffizienz und kürzeren Zykluszeiten.

PacTech bietet Lösungen für Fine-Pitch-Flip-Chips und WLCSP mit Cu-Pillar-Bumps an. Unser Cu-Pillar-Sortiment umfasst verschiedene Oberflächen mit individuellen Vorteilen:

Unsere Cu-Säulen sind optional mit Passivierung wie PI erhältlich und eignen sich für verschiedene Anwendungen wie 5G & RF, Automotive, Consumer, Power Controller und Sensor.