Elektrische Beschichtung für das Wafer Level Packaging

Elektrische Beschichtung für das Wafer Level Packaging

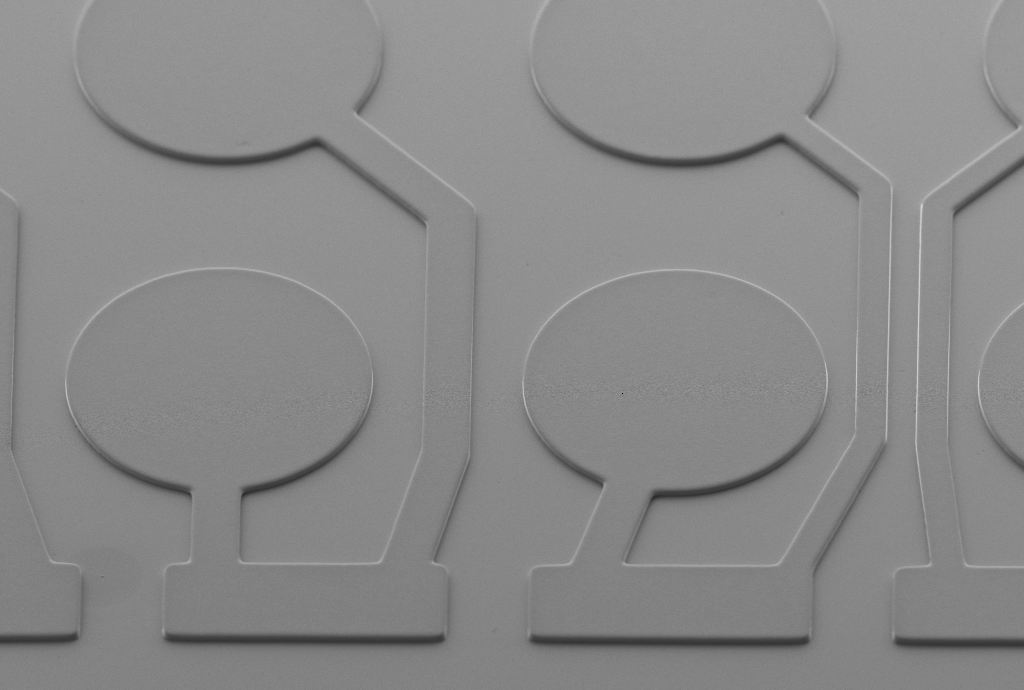

Das Wafer Level Chip Scale Packaging (WLCSP) setzt sich immer mehr durch, da die Industrie immer kleinere und dünnere mikroelektronische Gehäuse verlangt. WLCSP ermöglicht kleinere Formfaktoren, verbesserte elektrische Leistung und eine relativ einfachere Struktur als herkömmliche Drahtbond- oder Interposer-Gehäusetechnologien. PacTech bietet hochmoderne Wafer-Bumping- und WLCSP-Lösungen wie RDL und Kupfersäulenbeschichtung: