WAFER LEVEL PACKAGING-DIENSTLEISTUNGEN FÜR 3D IC, FLIP CHIP, WLCSP UND MEHR

Als Pionier auf dem Gebiet der stromlosen Beschichtung von Wafern bietet PacTech seit über 25 Jahren WLP-Dienstleistungen für die Halbleiter- und Elektronikindustrie an. Wir haben unsere WLP-Kapazitäten ständig erweitert und Spitzentechnologien entwickelt, um Gehäuse mit höherer Dichte und kleinerer Größe zu unterstützen.

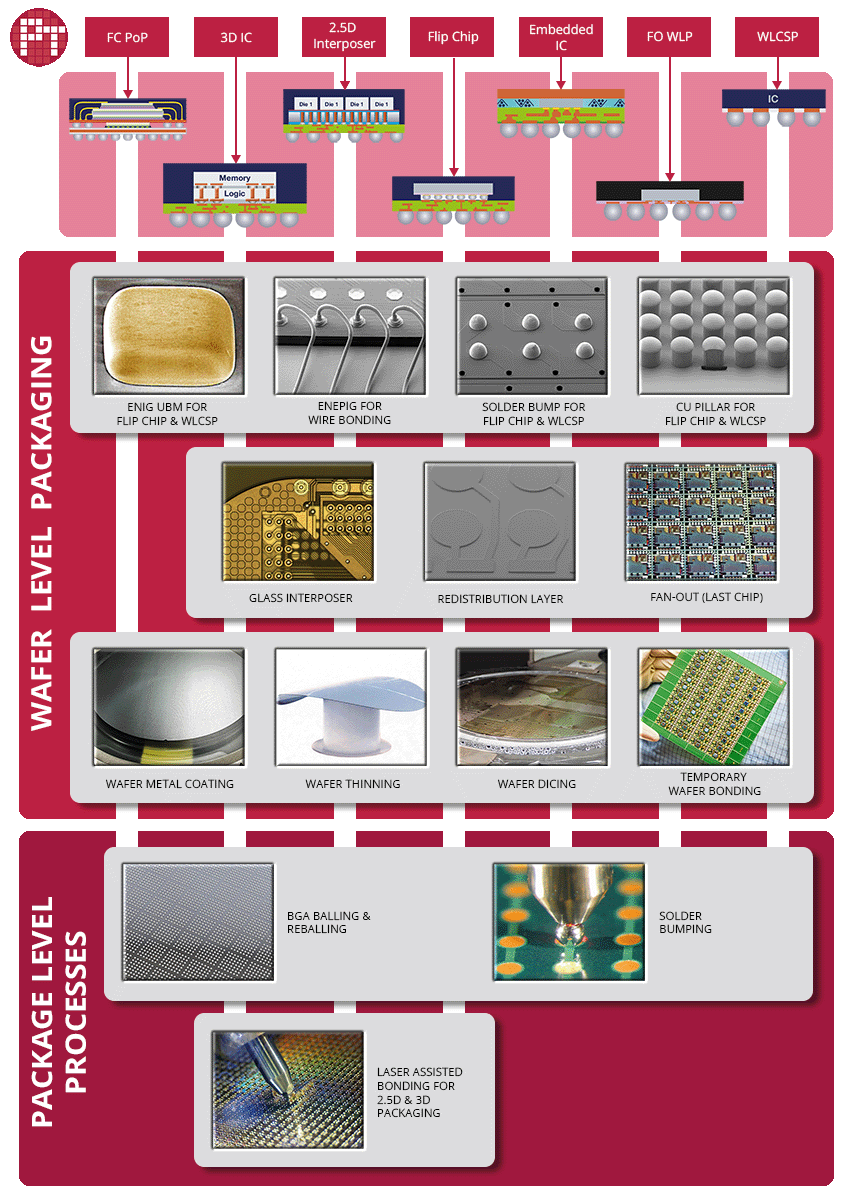

Wir bieten verschiedene Metallisierungsverfahren an, darunter galvanische Beschichtung, stromlose Beschichtung, Sputtern und Aufdampfen. Es gibt verschiedene Möglichkeiten des Lötbumpings, wie z. B. Lötdruck, Ball-Placement, elektroplattierte Lötbumps und Cu-Pillar, die auf spezifische Layout- und Montageanforderungen abgestimmt sind.

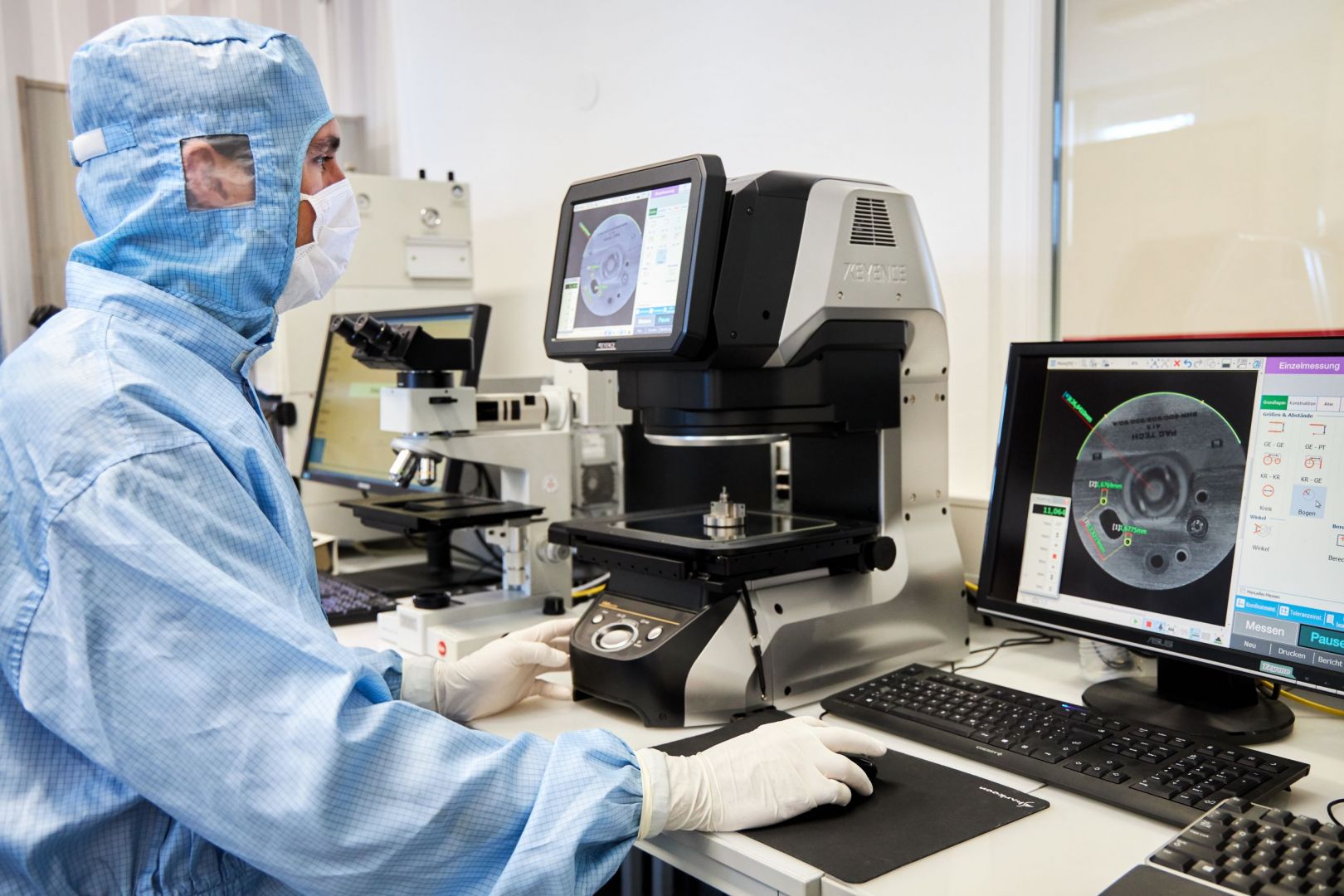

Darüber hinaus verfügt PacTech über modernste Mess- und Analysegeräte, die den Entwicklungs- und Produktionsprozess unterstützen, darunter: Röntgen, Schertest, AOI, FIB, SEM, Hochgeschwindigkeitskugelziehen, chemische Analyse usw.

Wir bieten WLP-Dienstleistungen weltweit von allen drei PacTech-Standorten in Europa, Amerika und Asien aus an. Unsere professionellen WLP-Spezialisten empfehlen die leistungsfähigsten und kosteneffizientesten Lösungen und unterstützen die Entwicklung kundenspezifischer Prozesse außerhalb der Standardangebote.

Unser zertifizierter WLP-Servicestandort in Europa erfüllt die notwendigen Sicherheitsanforderungen gemäß internationalen Sicherheitsvorschriften für den Umgang und die Verarbeitung sensibler und streng vertraulicher Kundenprodukte.

Unsere WLP-Dienstleistungen werden in einem breiten Spektrum von Industrieanwendungen eingesetzt, darunter Automobil, Luft- und Raumfahrt, Landwirtschaft, Handel, Kommunikation, industrielle Energieversorgung, 5G und RF und viele mehr. Sie sind für zahlreiche Montage- und Verpackungsanwendungen geeignet, wie z. B.:

- Flip-Chip-Gehäuse auf Gehäuse (FC PoP)

- 3D Integrierte Schaltung (IC)

- 2,5D-Interposer

- Flip-Chip

- Eingebetteter integrierter Schaltkreis (IC)

- Fan-Out Wafer Level Packaging (FO WLP)

- Wafer Level Chip Scale Packaging (WLCSP)